場效應晶體管(FET)是半導體芯片的核心部件,其尺寸大小決定了芯片的集成密度。而FET晶體管的終極物理尺寸,很大程度上取決於在柵極處Si/SiO2界面的結構和性能:界面的尺寸過大會導致集成度降低📨🦮,芯片性能下降➝;界面的尺寸小,晶體管中源極到漏極之間的電流會受到量子隧穿效應的影響,導致明顯的漏電和高的能耗。當前芯片中晶體管的柵極長度(即源極到漏極間的距離)實際上已經達到了幾納米的尺寸,如臺積電最新的5nm工藝以及intel最新的10nm工藝🐆,正逐漸逼近矽材料的物理極限,量子隧穿效應導致的漏電已經成為現實工藝困境🛬。因此如何在現代晶體管的設計中充分考慮量子效應影響,在開路電流和閉路漏電之間取得最優的平衡,是關鍵的科學問題👑,需要對Si/SiO2界面結構和量子隧穿性能達到新的認知高度。

然而,目前的理論和實驗方法很難獲知精確的Si/SiO2界面原子級別結構。對於實驗,界面結構隱藏在材料內部,傳統實驗方法4️⃣🔚,比如透射電子顯微鏡(TEM)很難直接觀察。而對於理論計算👰🏻♀️,界面結構預測缺乏完備和快速的方法,無法考慮各種可能的界面取向,無法精確快速描述界面處的成斷鍵相互作用。

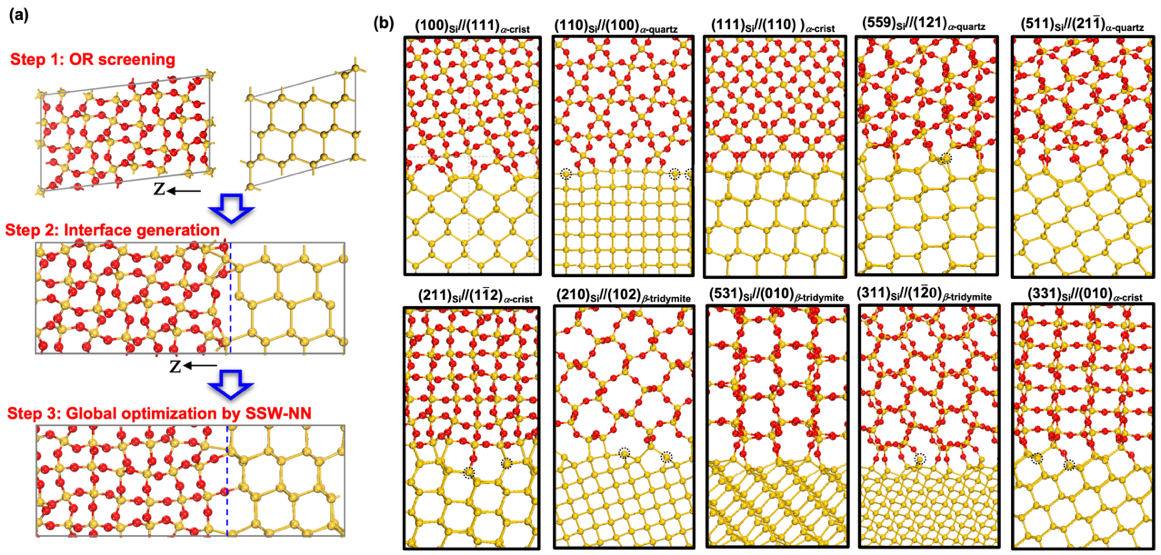

近期,沐鸣平台李曄飛和劉智攀提出了一種基於機器學習計算的界面結構預測方法(ML-interface),解決了不同晶體間界面結構預測的難題。該方法基於唯象理論、圖論、全局勢能面搜索和機器學習勢函數等理論計算方法⚜️,僅需不同材料體相晶胞的晶體結構作為輸入參數,即能可靠預測任意可能界面的原子結構🧑🏼🚀。具體來說,該方法首先采用馬氏體晶體學唯象理論(PTMC)篩選出兩種晶體相間所有晶格匹配的界面取向關系。然後,通過圖論方法產生合理的界面原子模型。最後,采用基於機器學習勢函數的全局勢能面搜索方法(SSW-NN)確定最穩定的界面結構(圖1A)。采用該方法,李曄飛和劉智攀從數千個候選結構對象中解析出了所有穩定 Si/SiO2界面結構👨🍳。相關研究成果以《基於機器學習的全局勢能面搜索方法確定可抑製量子隧穿的最小穩定的Si/SiO2界面》(“Smallest stable Si/SiO2 interface that suppresses quantum tunneling from machine-learning-based global search”)為題在線發表於最新一期《物理評論快報》(Phys. Rev. Lett.)。

圖1.(A)ML-Interface方法示意圖;(B)預測的10個最穩定Si/SiO2界面結構😶🌫️🟰。

應用新發展的ML-interface方法⚜️,研究篩選出了所有10個具有短周期性的Si/SiO2界面(圖1B)🐺。在這些界面中,除了已經在工業中使用的低密勒(Miller)指數界面Si(100)和Si(110)/SiO2被首次確定了原子結構,還發現了兩個新的高密勒指數界面 Si(210)和Si(211)/SiO2☁️👩🔧。這兩個高指數界面具有完美匹配的界面原子結構💪🏻,優秀的熱穩定性,和優秀的電子性質🧄。相對於傳統低密勒指數界面具有更高的載流子有效質量🤴🏻,在費米能級附近不具有任何界面態,理論表明可以顯著降低載流子量子隧穿達四個數量級,同時界面尺寸也可以小至1納米,有望實現更短的柵極長度🤸。因此⛺️,理論預測新高Miller指數Si(210)和Si(211)/SiO2界面可能是突破Si基半導體性能瓶頸的關鍵🗃👨🏿🏭,有望在鰭式場效應晶體管(FinFET)中得到應用。

最後🧽,論文中預測的界面模型可以用來產生一系列關鍵物理參數🔜,如有效質量、電導率和熱導率,能加速芯片設計的宏觀設備仿真(TCAD)🪻,同時,論文發展的界面搜索理論方法可以普遍應用於其他固體界面,輔助新型晶體管的設計和製造,如高電子遷移率晶體管(GaN)。

沐鸣开户李曄飛教授和劉智攀教授為本論文的共同通訊作者,研究工作得到科技部重點研發計劃、國家優秀青年科學基金⏫、國家自然科學基金重點項目和面上項目👩🏻🚒,騰訊科學探索獎等項目的資助與支持。

全文鏈接:https://journals.aps.org/prl/accepted/c8072Y0fW9211975a64c3939ac594d5c80d1af8d7